在芯片实验室的显微镜下,工程师们正与物理定律进行着一场无声的战争,每一次将电路缩小1纳米,都意味着一场价值数千亿的市场格局洗牌。

三星、SK海力士和美光三大巨头几乎垄断了全球市场,而竞争的焦点,正是那个以“1X”、“1Y”、“1Z”命名的工艺节点游戏-4。

这不仅仅是技术竞赛,更是商业生存战——1纳米的领先,可能直接转化为一年超过1.2万亿日元的销售额差异-4。

在普通用户看来,内存条就是一块绿色电路板加几个黑壳芯片。但在半导体工程师眼中,这里藏着人类最精密的制造艺术。

DRAM的基本存储单元由一个晶体管和一个电容组成,靠电容是否储存电荷来代表数据1或0-8。几十年来,行业遵循摩尔定律,不断缩小这些元件的尺寸-4。

但这里有个致命矛盾:电容可以缩小,但它必须储存足够量的电荷,否则1和0的区分就会变得模糊,导致存储功能失效-4。

这就是为什么DRAM制造商如此执着于“1纳米微缩”——他们必须在缩小一切的同时,想方设法让电容保持足够的电荷储存能力。

从平面型结构到堆栈型,再到沟槽型,都是为了在更小空间内维持电容的有效面积-4。如今,三大厂商都采用了“气缸型”电容结构,通过在晶体管上堆积绝缘膜、凿出深孔来形成电容-4。

当制程进入1X纳米领域时(大约相当于18-19纳米),一切变得更加挑战极限。

美光的1X纳米DRAM采用了6F²单元设计,结合了岛型交错主动层图案的鞍型块状鳍片(FinFET技术)、具有凹槽通道的埋入式金属字线等创新结构-1。

与上一代2Y纳米(约20纳米)产品相比,美光1X纳米DRAM的裸晶尺寸大幅缩小了约18.3%,使得存储密度得以提升-1。

你可能不知道的是,当我们说“18纳米DRAM”时,这个数字指的是DRAM中浅槽隔离间距的一半,这是目前DRAM中最精细的尺寸-4。

为了加工出这些微小的结构,现代DRAM制造中的深宽比已经达到了惊人的40-45,意味着孔的深度是其直径的40-45倍-4。想象一下,这相当于用一根吸管挖出一口深井的技术难度。

为什么三大巨头要在这场1纳米的赛跑中押上全部赌注?

答案藏在简单的数学中:当制程从2Y纳米进步到1X纳米,芯片尺寸缩小意味着同一片晶圆能切割出更多的芯片。

以当年的2Gb DRAM为例,三星的28纳米工艺芯片面积为45平方毫米,而美光的32纳米工艺芯片为60平方毫米-4。

这一微小差异导致三星每片晶圆可比美光多生产近500颗芯片-4。假设每颗芯片价值4美元,仅一片晶圆的销售差距就达2000美元-4。

放大到月产能50万片晶圆的工厂,年度销售额差距将超过120亿美元,换算成日元就是约1.2万亿日元-4。

这就是为什么每1纳米的推进都伴随着巨额研发投入和市场风险——这不是单纯的技术炫耀,而是生死存亡的商业决策。

随着DRAM 1X结构不断微缩,一个名为“RowHammer”的安全漏洞日益凸显-2。这个问题简单来说就是,反复访问(“锤击”)DRAM中的某一行,会导致相邻行的数据发生位翻转-2。

更小的制程工艺使DRAM对这一漏洞更加敏感-2。恶意程序可以利用这一点,通过触发大量的RowHammer防护操作,有效地占用内存系统,拖慢甚至瘫痪良性应用程序-2。

为解决这一问题,研究人员提出了BreakHammer方案,通过识别和限制可能触发RowHammer的线程,将系统性能平均提升了48.7%,同时将面积开销降至几乎为零-2。

在AI时代,这个问题变得更加棘手。攻击者可以利用RowHammer漏洞,精准翻转深度神经网络模型中的特定权重位,从而破坏AI推理的准确性-9。

针对这一威胁,研究人员开发了DNN-Defender等专门防御机制,利用DRAM内部交换技术保护神经网络权重,在不增加硬件开销的情况下有效抵御攻击-9。

当前DRAM 1X结构的发展正在接近平面微缩的物理极限,行业已将目光投向了三维堆叠。

NEO半导体提出的3D X-DRAM概念借鉴了3D NAND闪存的经验,通过垂直堆叠存储单元来突破密度瓶颈-6。这种技术有望将存储密度提升10倍以上,对AI和高性能计算领域具有重要意义-6。

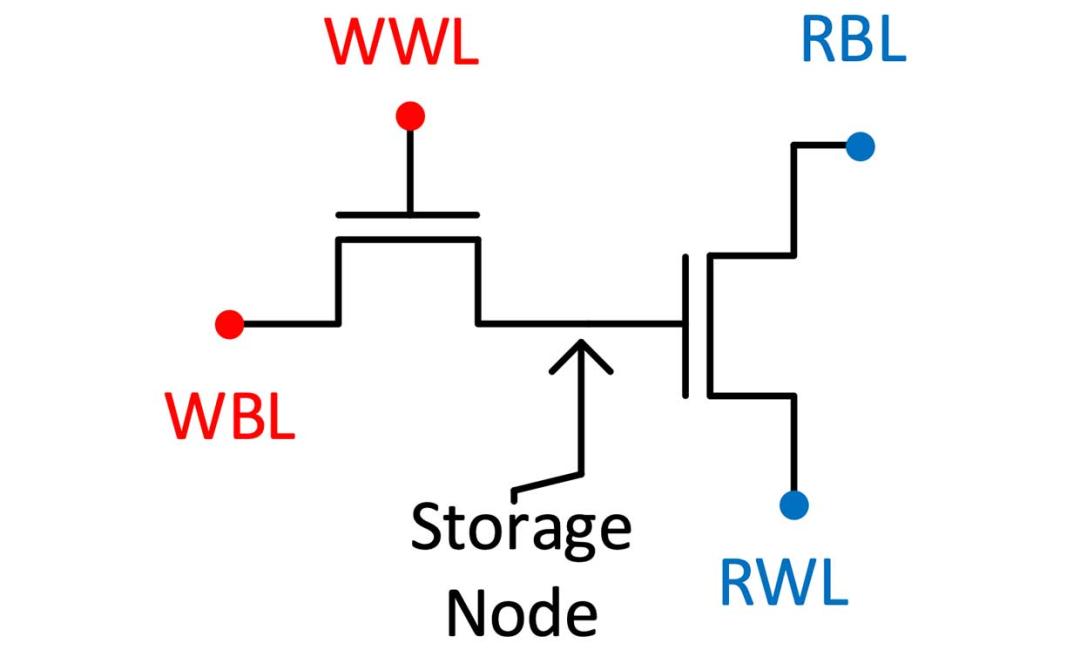

3D X-DRAM探索了多种单元结构,包括1T1C(单晶体管加电容)和3T0C(三晶体管无电容)等创新设计-6。特别是1T1C结构,采用新型材料可将数据保留时间延长至超过450秒,远超传统DRAM的毫秒级水平-6。

三星、SK海力士和美光也在积极推进各自的3D DRAM研发计划-6。这种从平面到立体的转变,可能彻底改变存储行业的游戏规则。

与此同时,美光已经推出了更先进的1β(1 beta)工艺,这是10纳米级别DRAM的第五代技术-10。与上一代1α相比,1β在能效上提高了约15%,在内存密度上提升了35%-10。

网友“芯片爱好者”提问: 我经常看到DRAM有1X、1Y、1Z这些代号,它们到底对应多少纳米?为什么不用具体数字而要用字母?

回答: 这个问题提得特别好,确实很多消费者会被这些字母搞糊涂。在DRAM行业,1X、1Y、1Z确实是制程节点的代号,它们大约分别对应18-19纳米、17-18纳米和16-17纳米-4。

为什么用字母而不是具体数字?一方面有技术保密的考虑,另一方面也反映了DRAM制程测量的特殊性。

你可能不知道,当我们说“18纳米DRAM”时,这个数字指的是DRAM中一种叫做“浅槽隔离”结构的间距的一半-4。这是DRAM中最精细的尺寸,但并不能完全代表整体技术水平。

用字母代号的另一个原因是,DRAM的制程微缩远比逻辑芯片复杂。它不仅要缩小晶体管,还要确保电容能储存足够电荷-4。每次微缩都是系统工程,字母代号更能体现代际演进的概念。

目前行业已经发展到1α、1β甚至1γ(伽马)阶段-10。美光最新的1β工艺比1α在能效上提高约15%,密度提升35%-10。这种渐进式的命名方式,帮助业界更清晰地追踪技术发展路径。

网友“硬件DIYer”提问: 下一代DDR5内存普遍采用了On-die ECC技术,这和传统的ECC有什么区别?真的能提升稳定性吗?

回答: 你注意到了内存技术的一个重要进步!On-die ECC(片上错误校正)确实是DDR5和LPDDR5的一大亮点,它与传统ECC有本质区别。

传统ECC需要在内存条上使用额外的DRAM颗粒来存储校验数据-5。而On-die ECC是在每个DRAM芯片内部完成的,不需要占用系统内存带宽-5。

随着DRAM制程从1X向1Y、1Z发展,单个存储单元越来越小,更容易受到各种干扰而产生错误-5。On-die ECC就像是给每个存储单元配了个“私人医生”,能够及时检测和纠正错误。

但要注意,目前的On-die ECC主要提供单错误纠正能力-7。随着错误率上升,未来可能需要更强大的校正方案,比如一些研究提出的新型ECC,能在不增加冗余的情况下纠正某些双位错误-7。

对于普通用户,On-die ECC确实能提升系统稳定性,特别是应对RowHammer等新兴威胁-5。但对于关键任务系统,许多仍会同时使用传统的模组级ECC,形成双重保护。

网友“科技投资者”提问: 目前DRAM市场被三大巨头垄断,中国厂商有机会突破吗?3D DRAM会不会是变局的关键?

回答: 这是一个很有战略眼光的问题。当前DRAM市场确实呈现三星、SK海力士和美光三足鼎立的格局,合计市场份额超过90%-10。但这并不意味着没有变局可能。

3D DRAM很可能成为游戏规则改变者。就像当年3D NAND闪存打破了平面NAND的格局一样,3D DRAM正在开辟新的技术赛道-6。

目前,三大巨头和新兴企业如NEO半导体都在积极研发3D DRAM技术-6。这种技术通过垂直堆叠存储单元,能够大幅提升存储密度,同时规避平面微缩的物理限制-6。

对于后来者,3D DRAM领域有几点机会:一是技术路径尚未完全固化,不同架构(如1T1C和3T0C)各有优势-6;二是可以借鉴相对成熟的3D NAND制造经验,降低学习曲线-6;三是新兴应用如AI和高性能计算对内存提出了全新要求,可能更愿意尝试创新方案-6。

值得注意的是,美光在最新技术中强调不使用EUV光刻机-10,这表明替代技术路径可能存在。对于资源相对有限的后来者,避开EUV这一资本密集型技术路线,可能是一种务实策略。

长远来看,中国厂商如果能在3D DRAM的某个细分领域形成突破,例如专注于AI优化的高带宽架构,是有可能找到市场切入点的。但需要做好长期投入的准备,这场竞赛既拼技术,也拼耐心和资金实力。