在深夜加班的电脑前,一次突如其来的蓝屏或游戏卡顿,可能正是一个名为TWR的时序参数在提醒你,它已经不堪重负。

内存的写入恢复时间(Write Recovery Time,简称 tWR 或 TWR)是内存控制器发出写入命令后,必须等待的最短时间,然后才能发出预充电命令-1。

这个看似微小的延迟参数,实际上是你电脑内存稳定性的守门人。它确保数据被可靠地写入内存单元,并为下一次操作做好准备。

你是否遇到过这样的情况:刚保存的文件突然丢失,游戏正酣时突然卡顿,或者系统毫无征兆地蓝屏?这些令人抓狂的瞬间,很可能与一个隐藏在内存深处的时序参数有关——它就是TWR。

在技术文档中,TWR被定义为“写入和预充电命令之间的延迟,以内存时钟周期数计算”-1。简单来说,当你向内存写入数据后,内存需要一点时间来“消化”这个操作,然后才能准备接收下一个指令。

这个等待时间就是TWR。如果太短,数据可能没有完全写入,导致损坏或丢失;如果太长,又会拖慢整体性能。

现代内存控制器需要精确设置TWR值,通常要求这个值必须匹配内存数据手册中定义的写恢复时间(tWR)-1。这可不是随便填个数字那么简单。

设置TWR就像走钢丝,需要在稳定性和性能之间找到微妙平衡。从技术角度看,TWR必须满足两个关键条件:TWR ≥ TRAS - TRCD 和 TWR ≥ TRC - TRCD - TRP-1。

举个例子,如果TRAS是4个周期,TRCD是2个周期,那么TWR必须至少为2个周期-1。这种情况下,TWR通常被编程为0x1(十六进制值)。

那些喜欢手动调整内存设置的玩家,经常会遇到TWR这个参数。在超频社区中,经验表明DRAM写入恢复时间通常设置在8-12个周期范围内-10。

这个值对内存带宽有轻微影响,但调整得当可以提升系统稳定性。有意思的是,当使用两个SDRAM设备时,两个内存控制寄存器必须用相同的TWR时序编程,而且这个值要对应最慢的那个SDRAM设备-1。

内存的稳定性不仅取决于我们如何设置它,还受到外界环境的影响。2023年的一项研究发现,热中子辐射会导致DDR4 DRAM组件的写入恢复时间退化-8。

在实验中,研究人员观察到tWR退化范围从1纳秒到超过15纳秒不等,后者足以导致内存故障-8。这种永久性的时序退化是由于热中子与硼-10相互作用产生的二次粒子造成的。

不同制造商的样品在退化截面上显示出高达8.9倍的差异-8。这意味着,在某些辐射环境下(如高空飞行、核医疗环境等),即使正确设置了TWR参数,内存仍可能因为环境因素而失效。

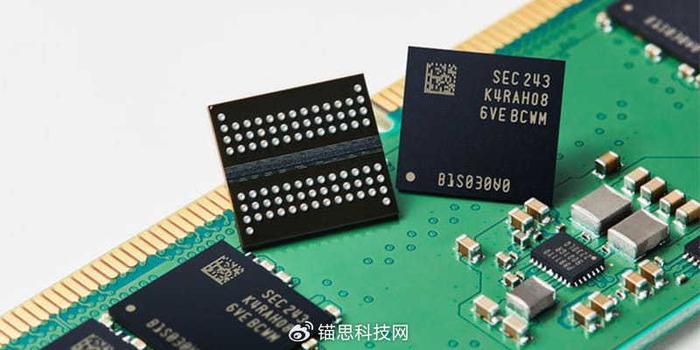

对于内存制造商而言,TWR测试是一项重大挑战。如何在保证测试质量的同时控制成本?Etron Technology在2003年提出了一种创新方案:使用低速测试器进行高速内存测试的方法-2。

他们的专利技术通过形成测试电路在内存芯片上,修改同步脉冲以产生具有受控导通时间的列选择信号,同时形成脉冲关闭发生器来修改具有受控关闭延迟的写入线路信号-2。

这种自定时方案可以根据DRAM单元的现场要求筛选写入恢复时间(tWR),允许使用低速测试器进行筛选-2。这种方法不仅降低了测试成本,还提高了测试灵活性。

随着DRAM技术进入深亚微米尺度,新的挑战又出现了。研究表明,DRAM单元恢复时间的显著变化会影响tWR等时序约束-3。

采用传统方法会导致低良率或大幅性能下降。一些创新方案试图通过构建具有不同访问速度的内存块,特别是利用快速块的性能优势,使内存控制器能够有效补偿因宽松时序约束而导致的性能损失-3。

对于大多数用户来说,不需要手动调整TWR参数。现代主板和内存模块已经通过其SPD(串行存在检测)芯片存储了推荐的时序设置,包括TWR。

当系统启动时,BIOS会自动读取这些值并应用它们。对于超频爱好者和专业用户,了解TWR的工作原理仍然很重要。

在实际应用中,如果你遇到内存相关的不稳定问题,可以尝试稍微增加TWR值。这会给内存更多时间完成写入操作,可能解决一些难以捉摸的稳定性问题。

但要注意,增加TWR值会轻微降低内存性能,因为内存需要等待更长时间才能进行下一次操作。

另一个值得注意的方面是,TWR与内存的预充电过程密切相关。半导体存储器装置通过在主银行结构中增加预充电控制部分,可以有效减少本地输入/输出线的预充电时间-5。

这种优化间接影响了TWR的实际效果,因为更快的预充电意味着写入恢复阶段可以更高效地完成。

当热中子辐射穿透DDR4芯片,TWR时间从1纳秒拉长到15纳秒,那个瞬间的内存单元正在经历一场微观世界的崩塌与重建-8。

制造商在测试仪器的滴答声中筛选亿万分之一秒的差异,而游戏玩家在屏幕前调整的每个参数,都连接着纳米尺度下电荷的艰难跋涉。